이번 주에 연례 핫 칩스 컨퍼런스가 열리면서 업계에서 가장 큰 칩 설계 회사 중 다수가 이 전시회에 참가하여 최신 제품 또는 곧 출시될 제품에 대해 이야기합니다. 인텔은 2024년에 출시될 차세대 제온 프로세서인 Granite Rapids와 Sierra Forest에 대해 이야기하기 위해 Hot Chips에 참석하고 있습니다. 인텔은 이전에 데이터 센터 로드맵에서 이 프로세서를 공개한 바 있으며, 가장 최근에는 올해 3월에 업데이트했으며, Hot Chips에서는 이 칩과 공유 플랫폼에 대한 기술적 세부 정보를 조금 더 자세히 제공하고 있습니다.

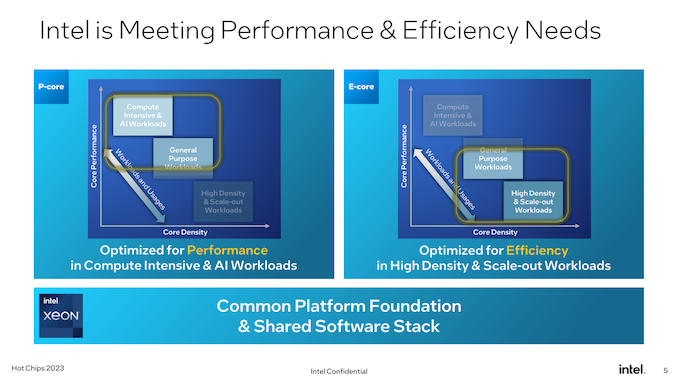

인텔의 제온 프로세서에서 “중요하지 않은” 세대는 없지만, 그레나이트 래피즈와 시에라 포레스트는 면적 효율적인 E-코어의 도입 덕분에 인텔의 제온 스케일러블 하드웨어 에코시스템에서 가장 중요한 업데이트 중 하나가 될 것으로 기대됩니다. 이미 12년부터 인텔의 소비자 프로세서의 주축을 이루고 있습니다.th 세대 코어(앨더 레이크)와 곧 출시될 차세대 제온 스케일러블 플랫폼은 마침내 인텔의 서버 플랫폼에 E-코어를 도입할 것입니다. 두 가지 코어 유형이 하나의 칩에 혼합되어 있는 소비자용 부품과 달리, 인텔은 순수하게 동질적인 전략을 추구하여 모든 P-코어 Granite Rapids와 모든 E-코어 Sierra Forest를 제공합니다.

데이터센터용 인텔 최초의 E 코어 제온 스케일러블 칩인 시에라 포레스트는 두 칩 중 가장 중요한 칩입니다. 그도 그럴 것이, 이 칩은 인텔의 EUV 기반 인텔 3 프로세스 노드를 위한 인텔의 주요 수단이며, 가장 먼저 출시된 제온이기도 합니다. 인텔에 따르면 2024년 상반기 출시가 예정대로 진행되고 있습니다. 한편 그래니트 래피즈는 동일한 인텔 3 공정 노드에서 “곧” 그 뒤를 이을 것입니다.

인텔이 한 세대에 서로 다른 두 개의 제온을 제공할 예정이기 때문에 차세대 제온 스케일러블 플랫폼의 가장 큰 요소는 두 프로세서가 동일한 플랫폼을 공유한다는 것입니다. 이는 동일한 소켓, 동일한 메모리, 동일한 칩렛 기반 설계 철학, 동일한 펌웨어 등을 의미합니다. 특히 AVX-512 지원과 관련하여 여전히 차이점이 있지만, 인텔은 이러한 칩을 최대한 호환 가능하게 만들기 위해 노력하고 있습니다.

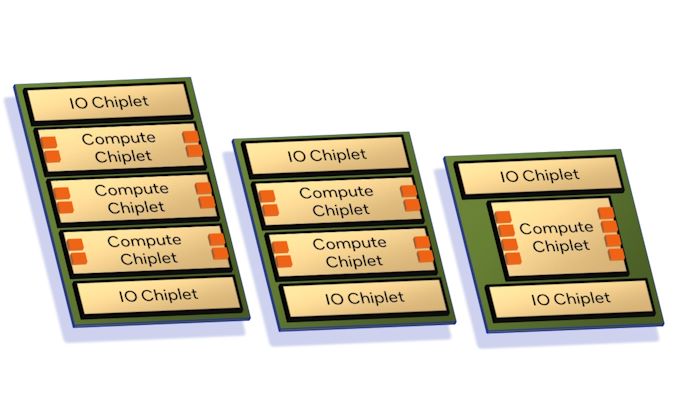

2022년에 인텔이 발표한 바와 같이, 그레나이트와 시에라는 모두 칩렛 기반 설계로, 인텔의 액티브 EMIB 브리지 기술을 사용하여 함께 스티칭된 컴퓨팅 및 I/O 칩렛의 혼합에 의존합니다. 인텔이 제온 분야에서 칩렛과 함께 춤을 추는 것은 이번이 처음은 아니지만(XCC 사파이어 래피즈가 그 영광을 차지했습니다), 이는 “완전한” 제온 칩렛을 함께 연결하는 대신 별도의 컴퓨팅/IO 칩렛을 사용함으로써 칩렛 설계의 뚜렷한 진화를 보여줍니다. 이는 무엇보다도 Granite와 Sierra가 공통 I/O 칩렛(인텔 7 프로세스에 기반)을 공유할 수 있다는 것을 의미하며, 제조 관점에서 볼 때 제온이 Granite인지 Sierra인지 여부는 단지 어떤 유형의 컴퓨팅 칩렛을 배치하는지에 대한 문제일 뿐입니다.

특히 인텔은 차세대 제온 스케일러블 플랫폼에 셀프 부팅 기능이 탑재되어 진정한 SoC가 될 것임을 처음으로 확인했습니다. 인텔은 작동에 필요한 모든 I/O 기능을 I/O 칩셋 내에 배치하므로 이러한 프로세서를 작동하는 데 외부 칩셋(또는 FPGA)이 필요하지 않습니다. 이로써 인텔의 제온 라인업은 한동안 비슷한 셀프 부팅 기능을 제공해온 AMD의 EPYC 라인업에 근접한 기능을 갖추게 되었습니다.

전체적으로 차세대 제온 스케일러블 플랫폼은 최대 12개의 메모리 채널을 지원하며, 현재 컴퓨팅 다이의 수와 성능에 따라 확장할 수 있습니다. 이전에 인텔이 공개한 바와 같이, 이 플랫폼은 새로운 멀티플렉서 결합 랭크(MCR) DIMM을 최초로 지원할 예정이며, 이는 기본적으로 두 세트/랭크의 메모리 칩을 묶어 DIMM과 주고받는 유효 대역폭을 두 배로 늘리는 것입니다. 더 빠른 메모리 버스 속도와 더 많은 메모리 채널의 조합을 통해 인텔은 이 플랫폼이 현재 사파이어 래피즈 제온보다 2.8배 더 많은 대역폭을 제공할 수 있다고 말합니다.

I/O의 경우, 최대 구성의 제온은 최대 136레인의 일반 I/O와 멀티 소켓 연결을 위한 최대 6개의 UPI 링크(총 144레인)를 제공할 수 있습니다. I/O의 경우, 이 플랫폼은 PCIe 5.0(왜 PCIe 6.0이 없을까요? 타이밍이 맞지 않았다고 들었습니다)과 최신 CXL 2.0 표준을 지원합니다. 전통적으로 인텔의 빅코어 제온이 그러했듯이, 그레이트 래피즈 칩은 총 8소켓까지 확장할 수 있습니다. 반면, 시에라 포레스트는 사용 중인 CPU 코어 수와 인텔이 고객에게 기대하는 다양한 사용 사례로 인해 최대 2소켓까지만 확장할 수 있습니다.

인텔은 공유 플랫폼에 대한 세부 사항과 함께 E코어와 P코어에 사용되는 아키텍처에 대한 개괄적인 개요도 처음으로 제공합니다. 현재 여러 세대의 제온에서 그랬던 것처럼, 인텔은 소비자 부품에 들어가는 것과 동일한 기본 CPU 아키텍처를 활용하고 있습니다. 따라서 Granite와 Sierra는 Meteor Lake 프로세서를 해체한 것으로 생각할 수 있으며, Granite에는 Redwood Cove P코어가 탑재되고 Sierra에는 Crestmont E코어가 탑재됩니다.

앞서 언급했듯이, 이것은 인텔이 제온 시장을 위한 E-코어를 제공하는 첫 번째 진출입니다. 이는 인텔이 이전 세대 E-코어 설계를 정의했던 소비자 중심 워크로드와 달리 데이터 센터 워크로드에 맞게 E-코어 설계를 조정하는 것을 의미했습니다.

아키텍처 자체에 대한 심층적인 분석은 아니지만, 인텔은 Crestmont가 6폭 명령 디코드 경로와 8폭 리타이어 백엔드를 제공한다고 밝혔습니다. 인텔의 P코어만큼 강력하지는 않지만 E코어는 결코 가벼운 코어가 아니며, 인텔의 설계 결정은 이를 반영합니다. 그럼에도 불구하고 그레나이트에 탑재될 P 코어보다 다이 공간과 에너지 소비 측면에서 훨씬 더 효율적이도록 설계되었습니다.

크레스트몬트의 L1 명령어 캐시(I-캐시)는 그레이스몬트와 동일한 크기인 64KB가 될 것입니다. 한편, 4코어 클러스터로만 제공되는 현재의 그레이스몬트와 달리, 크레스트몬트의 새로운 E코어 라인업에서는 코어를 2코어 또는 4코어 클러스터로 패키징할 수 있습니다. 이는 본질적으로 인텔이 CPU 코어에 대한 L2 캐시의 비율을 조정하는 방식으로, 구성에 관계없이 4MB의 공유 L2가 제공되므로 2코어 클러스터는 각 코어에 다른 방식보다 두 배 더 많은 코어당 L2를 제공합니다. 따라서 인텔은 칩 성능을 조정할 수 있는 또 다른 노브를 제공하므로, CPU 코어 수를 최대로 늘리는 대신 약간 더 높은 성능의 시에라 설계가 필요한 고객은 더 적은 수의 코어로 더 큰 L2 캐시에서 나오는 더 높은 성능을 얻을 수 있습니다.

마지막으로 시에라/크레스트몬트의 경우, 이 칩은 그레나이트 래피즈와 가능한 한 명령어 패리티에 가까운 성능을 제공할 것입니다. 즉, BF16 데이터 유형 지원은 물론 AVX-IFMA 및 AVX-DOT-PROD-INT8과 같은 다양한 명령어 세트에 대한 지원을 의미합니다. AMX 매트릭스 엔진 외에 AVX-512를 지원하지 않는 유일한 기능은 인텔의 울트라 와이드 벡터 포맷으로, Crestmont의 기능 세트에 포함되지 않습니다. 궁극적으로 AVX10이 이 문제를 해결하는 데 도움이 되겠지만, 현재로서는 인텔이 두 프로세서 간의 패리티에 최대한 근접할 수 있는 수준입니다.

한편, 그레이트 래피즈에는 레드우드 코브 P코어가 있습니다. 제온 프로세서의 전통적인 핵심인 레드우드/그래나이트는 시에라 포레스트만큼 인텔에게 큰 변화는 아닙니다. 하지만 그렇다고 해서 가만히 앉아 있는 것은 아닙니다.

마이크로 아키텍처 측면에서 레드우드 코브는 크레스트몬트에서 보았던 것과 동일한 64KB I 캐시를 탑재하고 있으며, E-코어와 달리 이전 제품보다 2배 더 큰 용량을 제공합니다. 인텔이 히트율과 지연 시간의 균형을 맞추기 위해 I 캐시 용량에 손을 대는 경우는 드물기 때문에 이는 주목할 만한 변화이며 인텔이 아키텍처에 대해 더 많이 이야기하면 그 파급 효과를 지켜보는 것은 흥미로울 것입니다.

하지만 여기서 가장 주목할 만한 점은 인텔이 부동 소수점 곱셈의 지연 시간을 더욱 단축하여 4/5 사이클에서 단 3사이클로 줄였다는 점입니다. 이와 같은 근본적인 명령어 지연 시간 개선은 드물기 때문에 언제나 환영할 만한 일입니다.

그 외에 Redwood Cove 마이크로아키텍처의 나머지 하이라이트는 분기 예측과 프리페칭으로, 이는 인텔의 일반적인 최적화 목표입니다. 분기 예측을 개선하고 드물게 발생하는 미스 비용을 줄이기 위해 할 수 있는 모든 작업은 성능 측면에서 상대적으로 큰 성과를 거두는 경향이 있습니다.

특히 제온 제품군에 더 적용하기 쉬운 레드우드 코브용 AMX 매트릭스 엔진은 FP16 지원을 받고 있습니다. FP16은 이미 지원되는 BF16 및 INT8만큼 많이 사용되지는 않지만, AMX의 유연성을 전반적으로 개선합니다.

메모리 암호화 지원도 개선되고 있습니다. Granite Rapids의 Redwood Cove 버전은 사파이어 래피즈의 128개 키에서 2048개, 256비트 메모리 키를 지원합니다. 캐시 할당 기술(CAT)과 코드 및 데이터 우선순위 지정(CDP) 기능도 일부 개선되며, 인텔은 이전 구현에서 LLC/L3 캐시만 제어했던 것과 달리 L2 캐시까지 제어할 수 있도록 확장합니다.

궁극적으로 인텔은 곧 출시될 제온을 통해 2024년 이후를 대비할 수 있는 유리한 위치를 점하고 있다고 믿습니다. 최고급 P코어 제온의 성능을 개선하는 동시에 더 가벼운 CPU 코어를 많이 필요로 하는 고객을 위해 E코어 제온을 도입함으로써, 인텔은 하나의 공통 플랫폼을 공유하는 두 가지 CPU 코어 유형으로 전체 시장을 공략할 수 있다고 믿습니다.

그레이트 래피즈와 시에라 포레스트의 개별 SKU에 대해 이야기하기에는 아직 이르지만, 인텔은 전반적으로 코어 수가 증가하고 있다고 밝혔습니다. 그래닛 래피즈 부품은 사파이어 래피즈보다 더 많은 CPU 코어를 제공할 것이며(SPR XCC의 경우 60개에서 증가), 물론 시에라는 144개의 코어로 그보다 더 많은 코어를 제공할 것입니다. 그러나 인텔은 코어 수에 따라 두 CPU 제품군을 세분화하지 않을 것이며, 시에라 포레스트는 더 적은 코어 수로도 제공될 것입니다(AMD의 EPYC Zen4c 베르가모 칩과 달리). 이는 P 코어와 E 코어의 서로 다른 성능 기능을 반영하며, 의심할 여지없이 인텔은 칩렛 사용으로 인한 확장성을 완전히 수용하고자 합니다.

시에라 포레스트는 이미 144개의 CPU 코어를 탑재할 예정이지만, 인텔은 사전 브리핑에서 첫 번째 E 코어 제온 스케일러블 프로세서의 코어 수를 더 늘릴 수도 있었다는 흥미로운 언급을 했습니다. 하지만 인텔은 코어당 성능에 좀 더 우선순위를 두기로 결정했고, 그 결과 내년에 출시될 칩과 코어 수가 결정되었습니다.

무엇보다도, 그리고 아마도 핫 칩을 위해 마케팅이 너무 오래 운전대를 잡도록 내버려둔 채로, 인텔은 차세대 제온 프로세서가 2024년 출시를 목표로 순조롭게 진행 중이라는 사실을 강조하고 있습니다. 인텔은 이제 막 사파이어 래피즈의 대규모 지연(그리고 에메랄드 래피즈에 대한 노크 효과)에서 회복하고 있기 때문에 그래닛 래피즈와 시에라 포레스트가 인텔의 타이밍이 다시 정상 궤도에 오를 것이라는 확신을 고객에게 심어주고자 노력하고 있습니다. 이전 제온 출시가 지연되고 E코어 제온 스케일러블 칩을 출시하는 데 오랜 시간이 걸리면서 인텔은 예전처럼 데이터 센터 시장에서 우위를 점하지 못했기 때문에 그래닛 래피즈와 시에라 포레스트는 향후 인텔의 데이터 센터 제품에서 중요한 변곡점이 될 것으로 보입니다.